作者:UnitedSiC资深员工与研发工程师Zhongda Li博士

简介在电动机控制等部分应用中,放缓开关期间的dV/dt非常重要。速度过快会导致电动机上出现电压峰值,从而损坏绕组绝缘层,进而缩短电动机寿命。在本应用说明中,来自UnitedSiC 的Zhongda Li比较了三种不同的dV/dt控制方法。

Zhongda Li博士于2007年获得北京大学理学士学位,于2013年获得伦斯勒理工学院电气工程博士学位。他拥有10余年的SiC和GaN器件技术研究经验。他曾发表过30

dV/dt开关降低硅MOSFET、IGBT和SiC MOSFET的开关dV/dt的传统方法可能会提高外部栅极电阻值。因为这些器件的CGD(CRSS)相对较高,所以外部RG值可以放缓dV/dt而不会过度延迟时间。对于图腾柱PFC等快速开关应用而言,这种方法非常好,在这种情况下,较快的dV/dt会带来较低的开关损耗。然而,对于电动机等较慢的应用而言,它可能需要非常高的电阻值。要将其放缓到5~8V/ns可能需要几千欧姆的栅极电阻,这可能会导致过长的开关延迟时间,进而导致步进速率低。对于位置控制应用,这可能会使性能受损。

有些方法可以将SiC FET器件的dV/dt有效控制在从45V/ns至5V/ns的范围内,而不会导致过长的延迟时间。这三种方法是:外部栅漏电容、器件RC缓冲电路和JFET直接驱动,它们需要在标准TO247-4L封装(UF3SC120009K4S)中使用UnitedSiC 9mΩ 1200V SiC FET,并在75A/800V下开关。

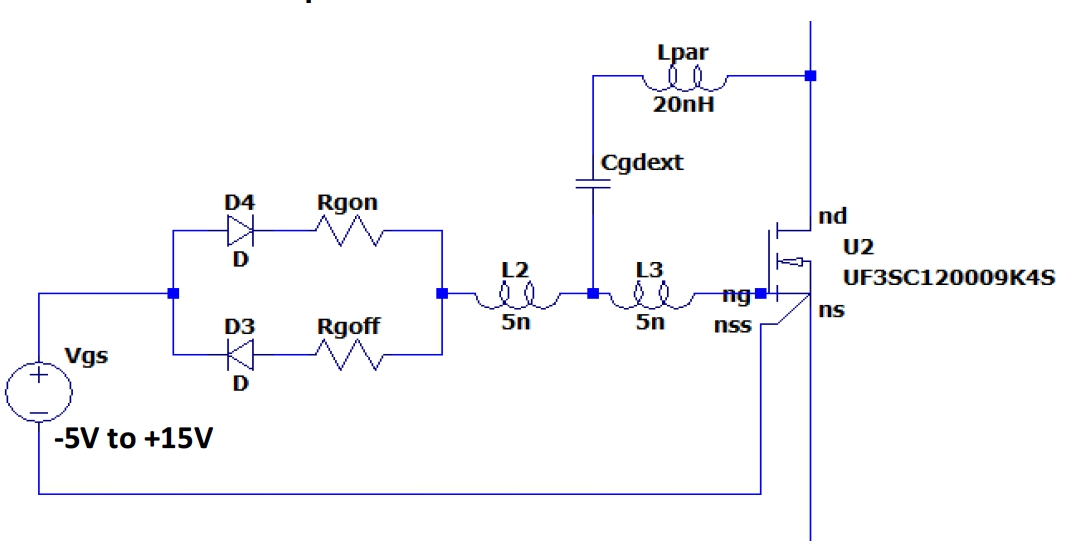

外部栅漏电容第一种方法是在半桥的高侧和低侧FET的栅极和漏极之间添加外部栅漏电容(CGD)。对于所选SiC FET,CGDEXT的值选定为68pF。我们故意将一个20nH的寄生电感与外部电容串联,以说明此方法对于路径中的寄生电感不敏感(图1)。

图1 带外部CGD的栅极驱动(在高侧和低侧FET上均有)以实现dV/dt控制

在使用独立器件的真实应用中,这种寄生电感应该远小于20nH,因为外部CGD可能会置于电路板上靠近FET的位置。然而,如果在模块内使用UnitedSiC FET芯片,并将外部CGD置于模块外,则路径中可能会存在20nH的寄生电感。

我们首先使用UF3SC120009K4S SPICE模块通过SPICE模拟优化外部CGD方法,然后使用双脉冲测试电路对其进行实验验证。68pF的外部CGD被有意焊接在TO247-4L的C引脚和D引脚之间,而不是电路板上,以提高路径中的寄生电感。

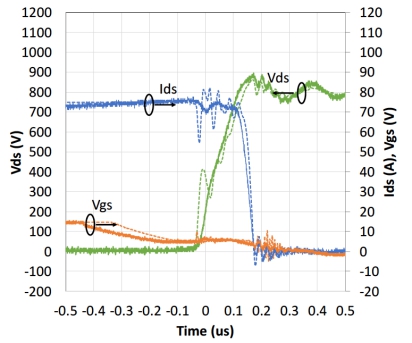

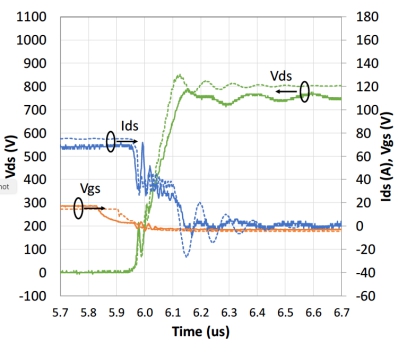

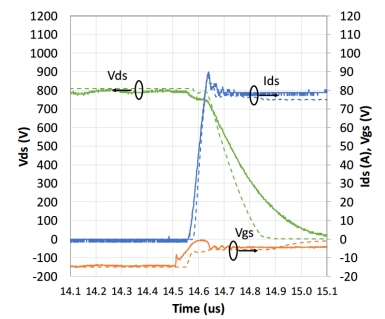

从实验测量和SPICE模拟中得到的关闭和打开波形被叠加在一起以进行比较。在图2中,测量波形和模拟波形非常吻合。

图2 实验测量(实线)和SPICE模拟(虚线)的关闭(左)和打开波形叠加(75A,800V,外部CGD为68pF,RG为33Ω)

在外部CGD为68pF的情况下,使用10Ω至33Ω的RG可以将dV/dt有效控制在25V/ns至5V/ns范围内。对于SPICE和实验,通过计算打开和关闭转换期间的IDS×VDS得到EON和EOFF,该值和预计一样随RG增加。

外部CGD可以容忍高寄生电感(在SPICE中为20nH)的原因是开关期间的电流非常小。对于外部CGD为68pF,dV/dt为8V/ns的情况,估计电流仅为0.54A且与SPICE模拟中的电流一致。因此,它适用于模块,在采用模块形式时,外部CGD置于模块外,位于电路板栅极驱动上,且路径中有一些寄生电感。

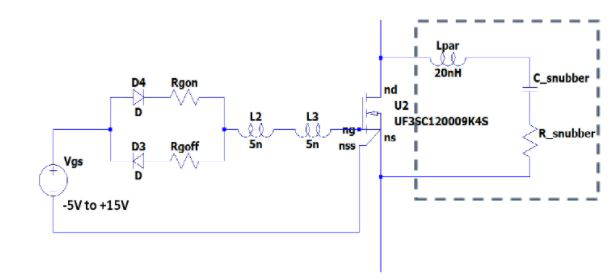

器件RC缓冲电路第二个dV/dt控制方法将RC缓冲电路与高侧开关和低侧开关并联。我们故意将一个20nH寄生电感与缓冲电路串联,旨在证明这种方法的缓冲电路路径中可以容忍寄生电感(图3)。

图 3 RC缓冲电路与FET并联(包括高侧和低侧FET)以实现dV/dt控制

在使用独立器件的真实应用中,RC缓冲电路可能非常靠近FET,且寄生电感仅为几nH。但是如果在模块内采用UnitedSiC FET芯片,则RC缓冲电路可以置于模块外,且路径中可能存在20nH的寄生电感。

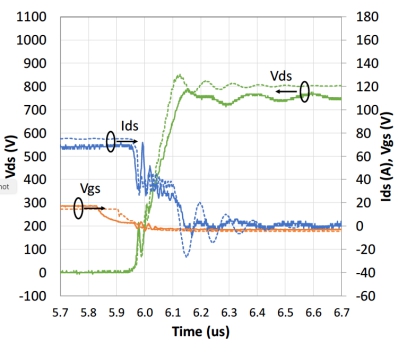

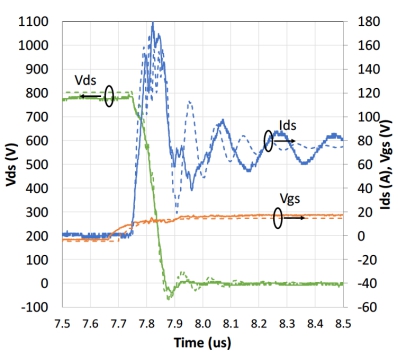

从实验测量和SPICE模拟中得到的关闭和打开波形被叠加在一起以进行比较(图4)。请注意,图表中的IDS电流包含缓冲电路电流。实验和SPICE模拟表明,dV/dt可以被最高5.6nF的C_SNUBBER(缓冲电路电容器)有效控制在50V/ns至5V/ns范围内。

图 4实验测量(实线)和SPICE模拟(虚线)的关闭(左)和打开波形叠加(75A,800V,RC缓冲电路为0.5Ω,5.6nF)

开关损耗(EON、EOFF和ESW)通过计算开关转换期间的IDS×VDS得到,其中IDS包括缓冲电路电流。因此,EON和EOFF中包含缓冲电路的损耗。然而,0.5Ω R_SNUBBER上的缓冲电路损耗非常低,尤其是当dV/dt较慢时。在C_SNUBBER为4nF,关闭dV/dt=8V/ns时,SPICE表明,缓冲电路损耗仅为0.2mJ,即在开关f=10kHz时为2W。我们发现,缓冲电路也能容忍高寄生电感(在SPICE中为20nH),因此,如果使用模块形式,RC缓冲电路可以置于模块外。

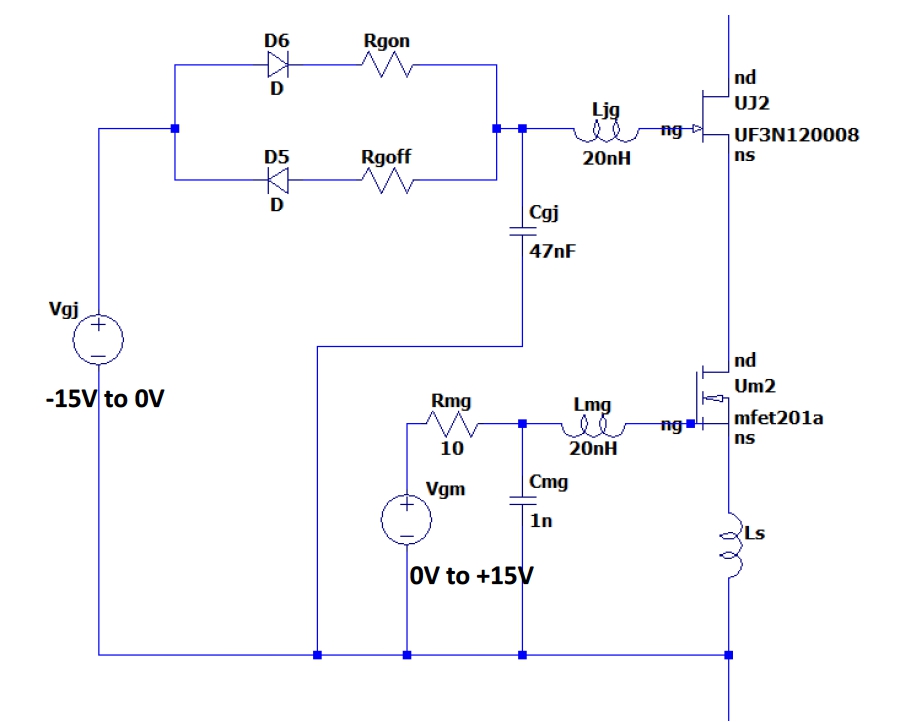

JFET直接驱动第三种方法是直接驱动,在这种情况下,Si MOS仅会在电路启动后打开一次,JFET栅极直接切换到-15V到0V之间(图5)。在这种配置中,常关操作会被保留,不过会需要栅极PWM和简单的“启用”信号。

在开关瞬态,高侧JFET保持关闭且电压为-15V,需要同步整流才能让续流JFET将第三象限中的通导损耗降低。

图5 JFET直接驱动方法(在高侧和低侧FET上均有)以实现dV/dt控制

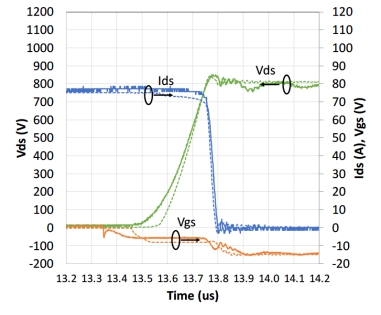

因为SiC JFET有可观的CRSS(CGD),所以一个4.7Ω的小RG就足以将dV/dt放缓至5V/ns。从实验测量和SPICE模拟中得到的关闭和打开波形被叠加在一起以进行比较(图6)。

图6 实验测量(实线)和SPICE模拟(虚线)的关闭(左)和打开波形叠加(75A,800V,JFET直接驱动且RG为4.7Ω)

SPICE(虚线)与实验(实线)波形间的IDS电流波形十分吻合。但是实验VDS波形表明其dV/dt比SPICE波形慢。原因可能是在dV/dt变换期间实验中使用的JFET栅极驱动器不能提供足够的栅极电流来为JFET CRSS充电和放电,导致dV/dt放慢。

将SPICE和测量得到的dV/dt进行比较会发现,可以将dV/dt很好地控制在15V/ns到4V/ns之间。使用与前两种方法相同的做法可以得到开关损耗,EON和EOFF和预计一样随着JFET RG增加。

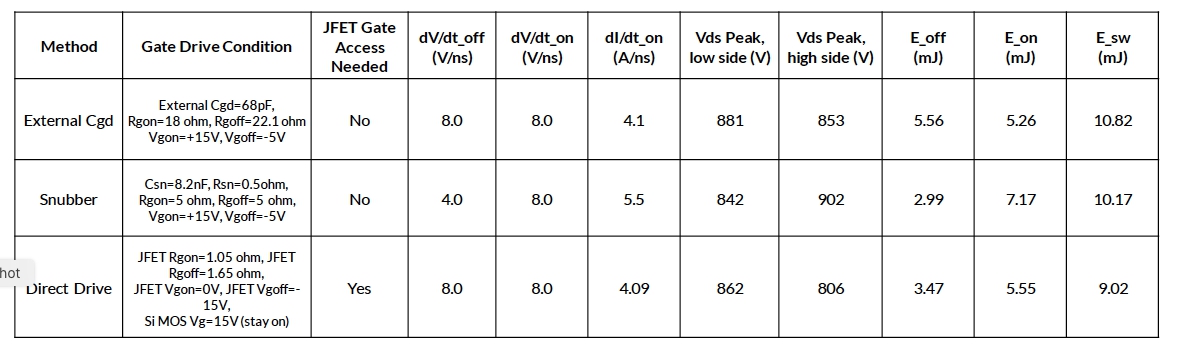

三种dV/dt控制方法比较在dV/dt ≤ 8V/ns这一相同限制下,使用SPICE模拟对这三种方法进行了比较(图1)。

表1 在dV/dt最大等于8V/ns的情况下,SPICE模拟的75A/800V开关下的性能

JFET直接驱动方法表现出的整体开关损耗最低,为9.02mJ。与其他两种方法相比,这种方法需要负压才能驱动SiC JFET,并且需要在电路启动时为Si MOS提供启用信号,从而增加了栅极驱动的复杂性。标准UnitedSiC FET不提供到JFET栅极的通路,但是新的双栅极TO247-4L产品正在开发中,既有SiC JFET栅极和Si MOS栅极,又适合JFET栅极驱动。这种方法还适合模块,可以添加单独的JFET栅极引脚。如此项研究所示,JFET栅极路径可忍受合理的寄生电感(在SPICE中为20nH),因此可以将JFET栅极驱动器放置在模块顶部的栅极驱动电路板上。

外部CGD和器件RC缓冲电路方法表现出了较高的开关损耗,但是它们不需要到JFET栅极的通路。当在独立封装(如TO247)中使用UnitedSiC FET时,两种方法都可以轻松实施到电路板上。由于这两种方法可以忍受合理的寄生电感(在SPICE中为20nH),它们还适合内部有UnitedSiC芯片的模块。

RC缓冲电路方法的一个缺点是它不能分别调整关闭和打开dV/dt。如表1所示,要实现8V/ns的打开dV/dt,关闭dV/dt必须降低至4V/ns,这会提高EOFF。

然而,外部CGD和JFET直接驱动方法使用单独的RGON和RGOFF,可以分别调整这二者。如表1所示,通过分别优化RGON和RGOFF,可以让打开和关闭dV/dt均为8V/ns。

总结总而言之,运用这些简单技术可以实现良好的dV/dt控制。较低的通导损耗和短路稳健性这两个UnitedSiC FET优势对于高效可靠的电动机驱动应用而言极为重要。

(采编:www.znzbw.cn)